|

|||||||||||||

| 网站首页 | | | 公司介绍 | | | 库存中心 | | | 品牌中心 | | | 新闻资讯 | | | 在线询价 | | | 联系我们 | |

|

||||||||||||||||||||||||||||

|

| IC库存索引: | A B C D E F G H I J K L M N O P Q R S T U V W X Y Z 0 1 2 3 4 5 6 7 8 9 |

| 当前位置:首页 > 新闻资讯 |

|

|

AT24C1024BW-SH25-T 可擦除可编程只读存储器 ATMEL品牌代理 发布时间:2012/12/20 10:55:44

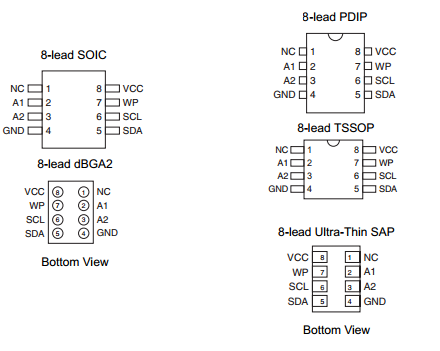

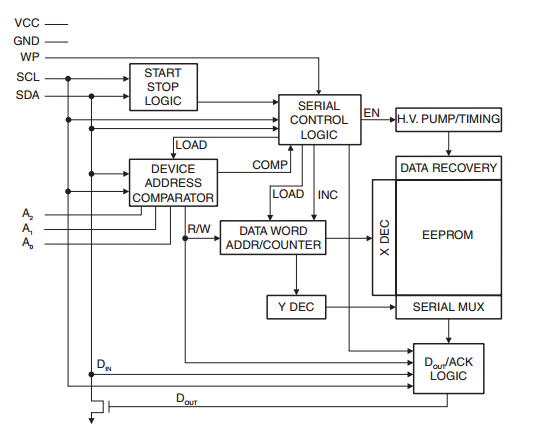

特点 •低电压操作 - 1.8V(VCC = 1.8V至3.6V) - 2.5V(VCC = 2.5V到5.5V) •内部结构131,072×8 •两线串行接口 •施密特触发器滤波抑制噪声 •双向数据传输协议 •400千赫(1.8V)和时钟频率为1 MHz(5V,2.5V) •写保护引脚的硬件和软件数据保护 •256字节页写模式(允许部分页写) •随机和顺序读模式 •自定时写周期(5 ms典型) •高可靠性 - 写次数:1,000,000次/页 - 数据保存:40年 •8引脚PDIP,8引脚JEDEC SOIC,8引脚EIAJ SOIC,8引脚TSSOP封装,8引脚超薄 小阵列(SAP),和8球dBGA2软件包 •模具销售:晶圆形式,磁带和卷轴 描述 AT24C1024B提供1,048,576位的串行电可擦除可编程只读存储器(EEPROM)组织为131,072词的8位的。 “ 设备的级联功能,允许最多四个设备共享一个共同的两线制总线。在很多工业和商业应用中,该器件经过优化的使用低功耗和低电压操作是必不可少的。该设备提供采用节省空间的8引脚PDIP,8引脚JEDEC SOIC,8引脚EIAJ SOIC,8引脚TSSOP封装,8球dBGA2和8引脚超薄SAP包。此外,整个环境可在1.8V(1.8V至3.6V)和2.5V(2.5V至5.5V)版本。   工作温度..................................-55°C至+125°C。

存储温度.....................................-65°C至+150°C

任何引脚电压

相对于地....................................-1.0V至+7.0 V

最大工作电压.......................................... 6.25V

DC输出电流............................................... ......... 5.0毫安

强调超越“绝对所列的最大额定值“,可能会造成永久性损坏设备。这是一种压力额定值仅为

该设备的功能操作在这些或任何以外的其他条件表明在本规范的业务部门是不暗示的保证。曝光绝对最大额定值长时间的状况可能会影响器件的可靠性。

引脚说明

串行时钟(SCL):在SCL输入时钟的上升沿数据到每个EEPROM设备和每个设备的时钟的下降沿将数据输出。

串行数据(SDA):SDA引脚的串行数据传输是双向的。此引脚是开漏输出,可与任何数量的其他漏极开路或集电极开路线或设备。

设备/地址(A1/A2):A1,A2引脚的器件地址输入,可以硬或不连接硬件兼容性与其他AT24CXX设备。当的A1,A2多达4个引脚是硬连接,1024K设备上最多可寻址的单总线系统(器件寻址详细讨论根据器件寻址部分)。如果A1/A2销被悬空,的A1/A2针将被内部拉低到GND的电容耦合到电路板的VCC平面<3 pF的。如果耦合>3 pF的,Atmel推荐连接A1/A2引脚连接到GND。写保护(WP):写保护输入,当连接到GND,允许正常的写操作。当WP连接到VCC,所有的内存写操作被禁止。

如果引脚悬空,WP引脚在内部拉低到GND的电容耦合到电路板的VCC平面<3 pF的。如果耦合>3 pF的,Atmel推荐连接引脚连接到GND。开关WP VCC到写操作之前创建了一个软件写保护功能。

|

|

||||||||