|

|||||||||||||

| 网站首页 | | | 公司介绍 | | | 库存中心 | | | 品牌中心 | | | 新闻资讯 | | | 在线询价 | | | 联系我们 | |

|

||||||||||||||||||||||||||||

|

| IC库存索引: | A B C D E F G H I J K L M N O P Q R S T U V W X Y Z 0 1 2 3 4 5 6 7 8 9 |

| 当前位置:首页 > 新闻资讯 |

|

|

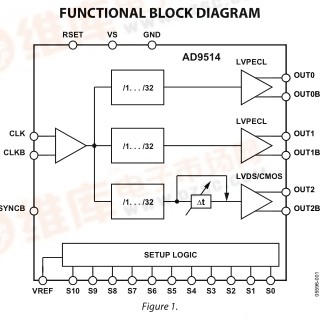

AD9514BCPZ原装现货热销/ADI品牌代理/价格/图片/PDF 发布时间:2014/10/13 9:39:04 概述 该AD9514采用了多路输出时钟分配IC在 设计强调低抖动和相位噪声最大化 数据转换器的性能。与其他要求苛刻的应用 相位噪声和抖动要求也受益于本部分。 有三个独立的时钟输出。两个输出端的 是LVPECL和第三输出可设置为LVDS或 CMOS电平。 LVPECL输出工作于1.6 GHz的,而 第三个输出工作在800 MHz的LVDS模式下,并 250兆赫的CMOS模式。 每个输出都具有可编程除法器,可以被设置为 用整数范围从1到32的一组选定的鸿沟 一个时钟输出的相对相位与其它时钟输出可 可通过分频器相位选择功能,作为手段设置 粗定时调整。 该LVDS/ CMOS输出的特点有三个延时元件 可选择的满量程延迟值(1.5纳秒,5纳秒,和10纳秒),每个 有16个步骤微调。 的AD9514不需要外部控制器 操作或设置。该装置是由装置编程 11引脚采用4电平逻辑(S0到S10)。编程引脚 内部偏置为⅓比。 VREF引脚提供的水平 ⅔比。 VS(3.3V)和GND(0V)提供另外两个逻辑电平。 该AD9514非常适合于数据转换器时钟 应用中最大的变频器性能 通过编码信号与亚皮秒抖动来实现的。 该AD9514可在一个32引脚LFCSP封装,工作 采用3.3 V单电源。温度范围为-40°C至+85°C。

特点

1.6 GHz差分时钟输入

3可编程分频器

除以在范围1跳转到32

相选择粗延迟调整

2个独立的1.6 GHz的LVPECL时钟输出

添加剂的宽带输出抖动225 FS RMS

1个独立的800兆赫/250 MHz的LVDS/ CMOS时钟输出

添加剂的宽带输出抖动300 FS RMS /290 FS RMS

时间延迟到10纳秒

设备配置有4个电平逻辑引脚

节省空间的32引脚LFCSP封装

应用

低抖动,低相位噪声时钟分配

时钟高速ADC,DAC的,DDS中,DDC的,DUCS,MxFEs

高性能无线收发器

高性能仪表

宽带基础设施

ATE

|

|

||||||||