|

|||||||||||||

| 网站首页 | | | 公司介绍 | | | 库存中心 | | | 品牌中心 | | | 新闻资讯 | | | 在线询价 | | | 联系我们 | |

|

||||||||||||||||||||||||||||

|

| IC库存索引: | A B C D E F G H I J K L M N O P Q R S T U V W X Y Z 0 1 2 3 4 5 6 7 8 9 |

| 当前位置:首页 > 新闻资讯 |

|

|

TPS73633DBVR低压差稳压器 - LDO 进口原装正品 美国TI公司产品 发布时间:2013/1/5 12:12:11

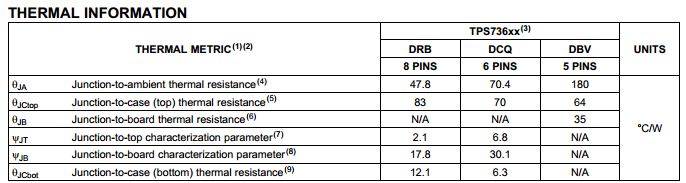

(1)有关传统和新的热度量的更多信息,请参阅IC封装热度量应用报告,SPRA953A。

(2)有关此设备PCB铜的面积的基础上的热估计,看到TI PCB热计算器的。

(3)热的数据,DRB,DCQ,和DRV包是通过热模拟得到的根据JEDEC标准方法的在JESD51系列指定。在模拟中使用了以下假设:

(一)我。 DRB:暴露的焊垫连接到PCB的接地层通过一个2x2的热过孔阵列。

(二) DCQ:裸露焊盘连接到PCB的接地层通过一个3x2散热通孔阵列。 III。 DBV:有没有裸露焊盘的DBV包。

(b)我。 DRB:顶部和底部的铜层被假设为具有20%的导热率的铜占20%的铜

覆盖范围。

(二) DCQ:顶部和底部的铜层中的每一个具有一个专用的20%的铜覆盖的图案。

III。 DBV:顶部和底部的铜层被假设为具有20%的导热率的铜占20%的铜

覆盖范围。

(三)这些数据产生在一个JEDEC的高-K(2S2P)板3英寸×3英寸的铜区的中心只有一个单一的设备。对

了解的铜面积热性能的影响,请参见本数据手册中的功率耗散部分。

(4)在自然对流的结点至环境的热阻是一个JEDEC标准,高K板在模拟中获得的,如指定在JESD51-7,JESD51-2a的在所述的环境中。

(5)的结点到外壳(顶部)的热阻是通过以下方式获得模拟冷板测试封装顶部。没有具体的JEDEC标准测试存在,但密切的描述可以在ANSI SEMI标准G30-88。

(6)结到电路板的热阻是通过模拟的环境中环冷板夹具控制PCB温度,如JESD51-8中描述。

(7)结到顶部的表征参数,YJT,估计在实际系统中的设备的结温,并提取从仿真数据获取QJA使用过程中描述JESD51-2a干扰素(第6和7)。

(8)结到电路板的表征参数,YJB,估计结点温度的设备,并在实际系统中提取从仿真数据获取QJA使用过程中描述JESD51-2a干扰素(第6和7)。

(9)结到外壳(底部)热阻是通过模拟冷板测试暴露(电源)垫。没有具体的JEDEC标准测试存在,但密切的描述中可以发现在ANSI SEMI标准G30-88。

TPS73633DBVR低压差稳压器 - LDO 进口原装正品 美国TI公司产品

|

|

||||||||