|

|||||||||||||

| 网站首页 | | | 公司介绍 | | | 库存中心 | | | 品牌中心 | | | 新闻资讯 | | | 在线询价 | | | 联系我们 | |

|

||||||||||||||||||||||||||||

|

| IC库存索引: | A B C D E F G H I J K L M N O P Q R S T U V W X Y Z 0 1 2 3 4 5 6 7 8 9 |

| 当前位置:首页 > 新闻资讯 |

|

|

AT45DB321D-SU原装现货 闪存 32M 8 I/O Atmel品牌 发布时间:2013/1/4 15:09:56

特点

●单2.5V - 3.6V或2.7V - 3.6V电源供电

●爱特梅尔®RAPIDS™ 串行接口:66MHz的最大时钟频率

●SPI兼容模式0和3

●用户可配置的页面大小

●每页512字节

●每页528字节

●页面大小可在工厂预先设定为512字节

●页面编程操作

●智能编程操作。

●8192页(512/528字节/页)主内存

●灵活的擦除选项

●页擦除(512字节)

●块擦除(4KB)

●扇区擦除(64KB)

●芯片擦除(32MB)

●两个SRAM数据缓冲器(512/528字节)

●允许接收的数据,而重新编程的闪存阵列

●连续读取功能,通过整个阵列

●代码映射应用程序的理想选择

●低功耗

●7毫安有效的读电流,典型的

●25μA典型待机电流

●15μA的深度掉电,典型的

●硬件和软件数据保护功能

●个别部门

●部门锁定的安全代码和数据存储

●个别部门

●安全性:128字节安全寄存器

●64字节用户可编程空间

●唯一的64字节的设备标识符

●JEDEC标准制造商和设备ID阅读

●10万次编程/擦除周期,最低每页

●数据保存时间:20年

●工业级温度范围

●绿色(以Pb/无卤化物/ RoHS标准)包装选项

1。描述

Atmel的AT45DB321D是2.5V或2.7V,串行接口,顺序存取快闪记忆体,非常适合于各种各样的数字语音,图像,程序代码,以及数据存储应用。 AT45DB321D支持Atmel的急流串行要求非常高的速度运行的应用程序接口。急流串行接口SPI兼容,频率高达为66MHz。 34603008位的内存为8,192页的512字节或528字节每个组织。在除了主内存,AT45DB321D还包含两个512/528字节的SRAM缓冲区。这些缓冲区允许接收的数据

而在主存储器中的页面进行重新编程,以及作为一个连续的数据流的写入。 EEPROM(电可擦除和可编程只读存储器)仿真(位或字节变性)是很容易处理一个自足的三个步骤的读 - 修改 - 写操作。不同于传统的快闪记忆体,随机访问多个地址线和并行接口,爱特梅尔的DataFlash®设备使用的急流城串行接口顺序访问

数据。简单的顺序访问极大地减少了引脚数,方便了硬件的布局,提高了系统的可靠性,最大限度地降低开关噪声,并减小封装尺寸。该器件经过优化,使用在许多商业和工业应用中,高密度,低引脚数,低电压和低功耗是至关重要的。要允许简单,在系统内可编程,的AT45DB321D并不需要高输入电压进行编程。 “器件采用单电源,2.7V到3.6V,为编程和读取操作。 AT45DB321D是通过片选引脚(CS)启用,并通过一个三线的串行输入(SI),串行输出接口,包括访问(SO)和串行时钟线(SCK)。所有的编程和擦除周期是自定时的。

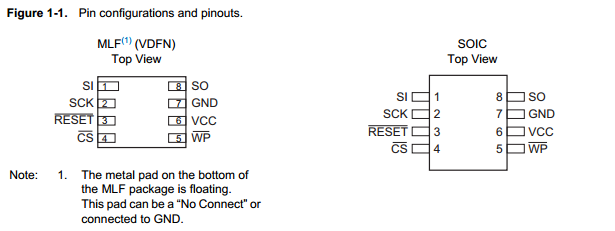

表1-1。引脚配置符号名称和功能断言国家类型

CS片选:断言CS引脚选择的设备。当CS引脚置为无效,

设备将被选中,并通常被放置在待机模式(不深的省电模式),和输出引脚(SO)将是在一个高阻抗状态。时,该设备是取消选择,数据将不被接受的输入引脚(SI)。在CS引脚上的一个高到低的过渡,才能启动的操作,从低到高过渡需要来结束操作。当结束一个内部自定时操作如编程或擦除周期,该设备将无法进入待机模式,直到完成上述操作。低输入SCK串行时钟:此引脚用于提供一个时钟的装置,以及用于控制数据和从该装置的流动。命令,地址,数据和输入数据上存在的SI针总是在SCK的上升沿锁存,而SO引脚上输出数据是

总的SCK的下降沿同步输出。

- 输入

SI串行输入:SI引脚是用来转移数据到设备。 SI引脚用于所有数据输入,包括命令和地址序列。 SI引脚上的数据总是锁定在SCK的上升沿。

- 输入

SO串行输出:SO引脚用于从设备到数据移出。 SO引脚上的数据

总是在时钟的SCK的下降沿。

- 输出

WP写保护:当WP引脚被置位,所有部门指定的保护对编程和擦除操作将受到保护,部门保护寄存器,

不管是否使能的部门保护命令已经发出,或不。 “WP引脚功能独立的软件控制的保护方法。后WP引脚变为低电平,扇区保护寄存器的内容不能被修改。如果一个程序或擦除命令发出到设备,而WP引脚被置,

器件将忽略该命令,不进行任何操作。设备将返回到

一旦CS引脚的空闲状态已被释放。使能扇区保护

然而,命令和部门锁定命令,将设备识别

当WP引脚被置位。

WP引脚内部上拉,悬空如果硬件控制

将不会被使用的保护。但是,它建议在WP引脚也可以

外部连接到VCC,只要有可能。

低输入

RESET复位:复位引脚(RESET)低状态将终止正在进行的操作,

复位内部状态机处于闲置状态。该装置将保持在复位

条件上的RESET引脚为低电平。可以正常运行

一旦恢复RESET引脚被带回到一个较高的水平。

该器件集成了一个内部上电复位电路,所以没有任何限制

RESET引脚上的电期间的序列。如果没有用到这个引脚和功能,它是

建议的RESET引脚外部驱动高。

低输入

RDY / BUSY就绪/忙:漏极开路输出引脚将被拉低时,该设备在忙内部自定时操作。该引脚,它通常是在一个高的状态(通过一个外部上拉电阻),将被拉低的编程/擦除操作过程中,比较操作,页面缓冲区传输。

忙状态表明闪速存储器阵列和一个缓冲器不能访问;读取和写入操作,仍然可以执行其他缓冲区。

- 输出

VCC

设备电源:,VCC引脚用于提供源电压的设备。

无效的VCC电压的操作可能会产生虚假的结果,不应该尝试。

- 电源

GND接地:接地参考电源。 GND应该被连接到系统接地。

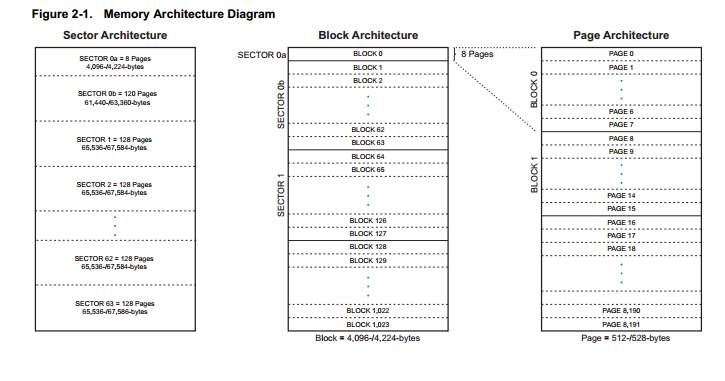

2。记忆体阵列

为了提供最佳的灵活性,AT45DB321D存储器阵列分为三个级别的粒度组成部门,块和页面。 “内存体系结构图”说明了每个级别的细分和细节的数量每扇区和块的页。所有的程序操作到的DataFlash设备出现在页逐页的基础。擦除操作可以执行芯片,扇区,块,或页级别。

|

|

||||||||